Due to a problem in the Intel® Quartus® Prime Standard Edition Software version 21.1 and earler, the Pin Planner displays incorrect differential pin pairs that can't be use for device migration in MAX® V devices.

When a migration device is added in the Migration Devices feature, the Pin Planner display only pins that can be used for device migration. When Show Differential Pin Pair Connections is enabled, it displays red lines that show differential pin pairs. But those red lines might not display differential pin pairs that can be used for device migration.

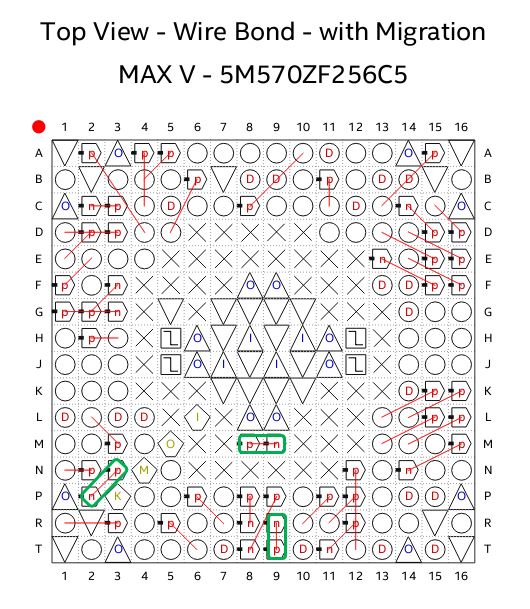

For example, when 5M570ZF256 is selected as a current device, 5M1270ZF256 is selected as a migration device, and Show Differential Pin Pair Connections is enabled, the Pin Planner shows the following diagram. Although there are many red lines for differential pin pairs, only the differential pin pairs enclosed by green can be used for device migration.

Figure 1. Pin location diagram in the Pin Planner

To work around this problem, manually check if both pins of each differential pin pair have the same pin locations and the same polarity between a current device and a migration device by comparing the pin-out files.

In pin-out files of MAX® V devices, find the Emulated LVDS Output Channel column that displays the name of the differential pin. DIFFIO_<symbol>p and DIFFIO_<symbol>n are a differential pin pair. For example, DIFFIO_L1p and DIFFIO_L1n are a differential pin pair.

The following are examples of how to check if a differential pin pair can be used for device migration:

- In 5M570ZF256, Pin C2 is DIFFIO_L1n and Pin C3 is DIFFIO_L1p. But in 5M1270ZF256, Pin C2 is DIFFIO_L1n and Pin C3 is DIFFIO_L2p. They are not a differential pin pair in 5M1270ZF256. The pin pair of C2-C3 can't be used for device migration.

- In 5M570ZF256, Pin R9 is DIFFIO_L11n and Pin T9 is DIFFIO_L11p. In 5M1270ZF256, Pin R9 is DIFFIO_L13n and Pin T9 is DIFFIO_L13p. The pin pair of R9-T9 is a differential pin pair and has the same polarity in both 5M570ZF256 and 5M1270ZF256. The differential pin pair of R9-T9 can be used for pin migration.

This problem has been fixed since Intel® Quartus® Prime Standard Edition Software version 22.1.