Visible to Intel only — GUID: iib1630367050192

Ixiasoft

Visible to Intel only — GUID: iib1630367050192

Ixiasoft

6.2. Register Map IP-XACT Support for Stratix® 10 EMIF DDR3 IP

When you generate an EMIF DDR3 design example from the Quartus® Prime software version 21.3 or later, the generated .ip file includes IP-XACT information for that IP. The generated IP-XACT information includes the register map for the DDR3 IP, Traffic Generator 2.0 (TG2), and Efficiency Monitor. The IP-XACT information for Stratix® 10 EMIF IP Memory-Mapped Registers (MMR) and Efficiency Monitor is included in ed_synth_emif_fm_0.ip, and the IP-XACT information for Traffic Generator 2.0 is included in ed_synth_tg.ip.

IP-XACT information is generated only with the design example. To enable generation of the IP-XACT information, follow these steps:

- To enable generation of the IP-XACT information for Stratix® 10 IP MMR, check the Enable Memory-Mapped Configuration and Status Register (MMR) Interface box on the Controller tab of the parameter editor.

Figure 43. Enabling IP-XACT Generation for MMR Registers

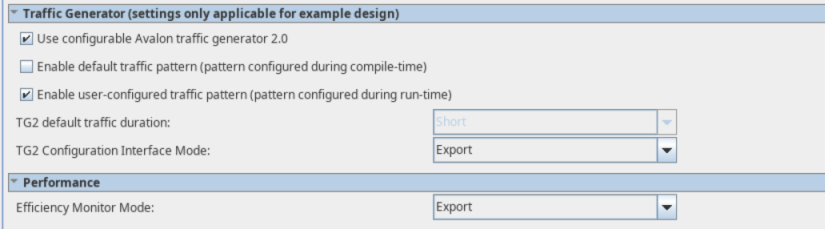

- To enable generation of IP-XACT information for TG2, check the Use configurable Avalon traffic generator 2.0 box and set TG2 Configuration Interface Mode to Export on the Diagnostics tab of the parameter editor. To include IP-XACT information for the Efficiency Monitor, set the Efficiency Monitor Mode to Export.

Figure 44. Enabling IP-XACT Generation for TG2 and Efficiency Monitor

For information on the registers available for the Stratix® 10 EMIF IP, refer to Stratix® 10 EMIF IP Memory Mapped Register (MMR) Tables in the End-User Signals chapter.

For information on the registers available for Traffic Generator 2.0, refer to Configuration and Status Registers in the Debugging chapter.

For information on the registers available for the Efficiency Monitor, refer to Control and Status Registers in the Debugging chapter.